CS 61C Summer 2018

Section 13: ECC/Parity, RAID, I/O

# Discussion 13: ECC/Parity, RAID, I/O

**Hamming ECC**

even parity = even # of I's

Recall the basic structure of a Hamming code. Given bits  $1, \ldots, m$ , the bit at position  $2^n$  is parity for all the bits with a 1 in position n. For example, the first bit is chosen such that the sum of all odd-numbered bits is even.

|   | Bit  | 1_        | 2  | 3          | 4         | 5  | 6  | 7  | 8         | 9  | 10 | 11         | 12 | 13 | 14  | 15  |

|---|------|-----------|----|------------|-----------|----|----|----|-----------|----|----|------------|----|----|-----|-----|

| - | Data | <u>P1</u> | P2 | D1         | <u>P4</u> | D2 | D3 | D4 | <u>P8</u> | D5 | D6 | D7         | D8 | D9 | D10 | D11 |

|   | P1   | X         |    | <b>*</b> × |           | X  |    | Ж  |           | *  |    | *          |    | X  |     | *   |

|   | P2   |           | ×  | X          |           |    | Ж  | *  |           | •  | *  | <b>X</b> < |    |    | *   | *   |

|   | P4   |           |    |            | X         | X  | X  | X  |           |    |    |            | X  | X  | X   | X   |

|   |      | l .       |    |            |           |    |    |    |           |    |    |            |    |    |     |     |

i. How many bits do we need to add to 00112 to allow single error correction?

ii. Which locations in 0011<sub>2</sub> would parity bits be included?

P2: 23,67 --iv. Write the completed coded representation for  $0011_2$  to enable single error correction.

000011

0000 & ham dist

v. How can we enable an additional double error detection on top of this?

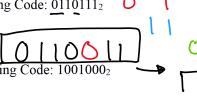

add I more bit to cover entire vi. Find the original bits given the following SEC Hamming Code: 0110111<sub>2</sub>

PI+P4 groups are wrong => error is at 1+4=5 vii) Find the original bits given the following SEC Hamming Code: 10010002

viii. Find the original bits given the following SEC Hamming Code: 0100110100001102

# **RAID**

Fill out the following table:

|    |        | Configuration                     | Pro / Good for                          | Con / Bad for                            |

|----|--------|-----------------------------------|-----------------------------------------|------------------------------------------|

| \$ | RAID 0 | Data disks                        | No over head,<br>fast read/wik          | No Redundancy                            |

| Ø. | RAID 1 | Mirrorng<br>Pata disk+ wpy        | Redundancy,<br>avall.<br>-fast recovery |                                          |

|    | RAID 2 | with bitwise pocity + pority disk | less<br>overhead<br>lowing<br>disk      | writing slaver<br>porty is<br>bottleneck |

|    | RAID 3 | byk wise parity<br>+ parity disk  | hrsk                                    |                                          |

| ₩  | RAID 4 | blockwise ganity<br>+ parity disk |                                         |                                          |

| 4  | RAID 5 | - no party disk                   | higher<br>writing<br>throughput         |                                          |

|    |        |                                   |                                         |                                          |

|    |        |                                   | pl V                                    | L V3                                     |

2

CS 61C Summer 2018

Section 13: ECC/Parity, RAID, I/O

# I/O

1. Fill this table of polling and interrupts.

| Pol  | ling    | hardware warts for data | frequent dorta<br>lower overhead<br>when handling<br>data | always waitny       |

|------|---------|-------------------------|-----------------------------------------------------------|---------------------|

| Inte | errupts | mygors, an              | infrequent date<br>other processes<br>while waiting "     | a<br>higheroverhead |

### 2. Memory Mapped I/O

Certain memory addresses correspond to registers in I/O devices and not normal memory.

### **0xFFFF0000 - Receiver Control:**

LSB is the ready bit, there may be other bits set that we don't need right now.

#### **0xFFFF0004 - Receiver Data:**

Received data stored at lowest byte.

#### **0xFFFF0008 - Transmitter Control**

LSB is the ready bit, there may be other bits set that we don't need right now.

#### **0xFFFF000C - Transmitter Data**

Transmitted data stored at lowest byte.

Write RISC-V code to read a byte from the receiver and immediately send it to the transmitter.